作者: 杜文张

当今社会是数据为王的时代,材料融合与异质异构是信息获取,数据处理的重要载体。尽管3D堆叠Chiplet晶粒成为后摩尔时代AI海量数据处理的主流技术路线之一,但仍需解决标准协议、3D建模、IP复用率低等诸多难题。因此,以3D封装技术为标志的3D异质异构、以材料外延工艺、IP设计灵活度高为特征的单片异质集成能否协同发展,推动集成芯片新技术创新是目前学术界、产业界共同关注的研究热点。

复旦大学张卫、吴春蕾教授团队携手江南大学黄伟教授团队,在兼容CMOS工艺的单片GaN异质集成芯片开展长期合作,在近期重要会议报道单片GaN/Si CMOS异质集成协同设计与重构技术研究工作。复旦大学集成电路与微纳电子创新学院研究生杜文张,承担本项目研究工作。

前 言

人工智能(AI)、机器学习(ML)与自动驾驶技术的飞速发展,催生了集成芯片前所未有的多功能化需求,而材料集成技术正是其重要支撑。为满足 AI/ML 系统严苛的供电与效率要求,基于GaN的功率变换器凭借 GaN 功率器件固有的低导通电阻与高电子迁移率特性,在转换效率与工作频率方面展现出显著优势。

受限于GaN集成水平,当前主流方案要么依赖面积较大的 PCB 级驱动方案,要么采用功耗较高的DCFL驱动电路。然而,采用引线键合实现硅基 CMOS 控制电路与 GaN 功率器件互连的板级平面集成(PCB)会面临开关频率受限的问题,这主要源于互连结构引入的高寄生参数。此外,GaN 基单片集成仍面临巨大的技术挑战:一方面是 GaN 中 P 型杂质难以有效激活,另一方面则是电子与空穴迁移率极度不匹配(空穴迁移率μp仅为 15 cm²/(V・s),而电子迁移率 μn高达2000 cm²/(V・s))。这种迁移率的不匹配会导致 GaN P 型与 N 型器件性能严重失衡,进而阻碍高性能互补逻辑集成电路的发展。

在此背景下,三维集成电路(3D-ICs)被视为实现 GaN/Si CMOS 异构集成的关键途径。凭借垂直堆叠结构,三维集成电路(3D-ICs)可显著提高器件密度,并降低整体功耗。然而,尽管三维集成电路(3D-ICs)具备显著的性能优势,但其也带来了前所未有的多维度热 - 应力耦合挑战。芯片堆叠层数的增加导致单位面积功率密度急剧上升,使得热量在堆叠内部积聚,形成常规冷却方式难以消散的局部热点。这些热点不仅会引发热应力、信号完整性下降、时序偏移等问题,还会直接危及芯片的长期可靠性。此外,层间大量的互连金属线会降低开关频率,并在高频工作模式下增加寄生损耗。材料与工艺集成相关的关键挑战已在我们之前的研究工作中得到解决。

一、异质集成工艺与协同设计

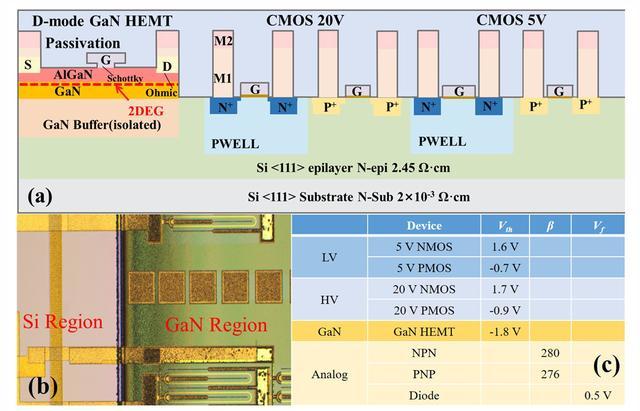

本文首先对我们去年报道基于 3 μm 20 V 工艺(包含低压 CMOS、高压 CMOS、GaN HEMT 及其他模拟器件)的 6 英寸 GaN/CMOS IC 单片异构集成方案进行了优化与系统研究,具体如图 1 所示。为满足集成芯片(尤其是模拟类集成芯片)的多样化应用需求,我们首次实现了模拟器件工艺与 GaN 材料集成的协同设计,突破了材料与工艺集成领域的关键技术壁垒。通过对 GaN HEMT 器件采用 ASM-HEMT 模型、对 Si CMOS 器件采用 BSIM4 模型,构建了异构集成系统的完整 SPICE 模型。与全 GaN 或全 Si 基技术及电路相比,本文协同设计的 GaN/Si CMOS 异构平台面向片上集成,能够实现更高的集成密度、更小的外形尺寸,并充分发挥 GaN 功率器件优异的开关速度特性,进一步验证了单片异构集成在器件复用性与电路定制化方面具有更显著的固有优势。该异构集成晶圆制备于一层N 型外延层之上,该外延层厚度范围为 7.25 至 7.75 μm,电阻率为 2.45–2.75 Ω・cm。此外延层生长在 6 英寸砷(As)掺杂硅(111)衬底上,该衬底电阻率约为 0.002–0.004 Ω・cm,非常适合 GaN 外延生长。

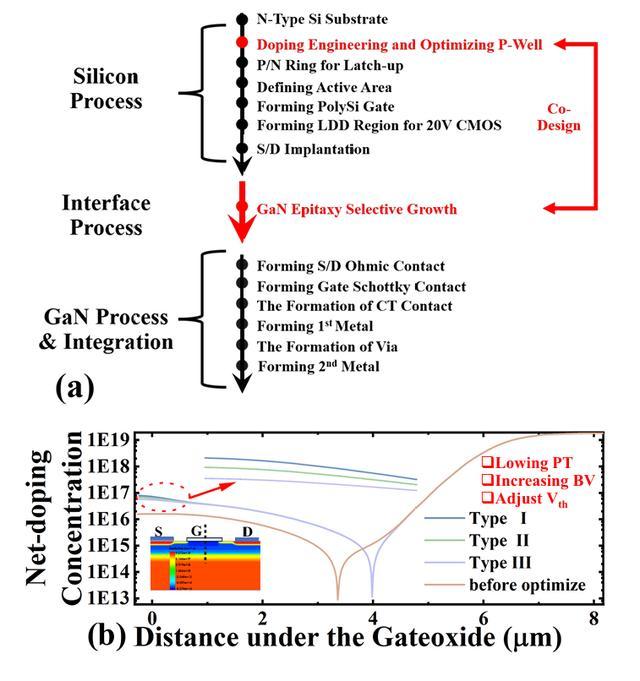

为满足不同半导体工艺的洁净度要求,并解决集成电路的器件多样性需求,所建立的 Si CMOS/GaN 异构集成平台工艺被划分为三个功能模块:硅工艺模块(模块 1)、界面工艺模块(模块 2)以及GaN 工艺与集成模块(模块 3),如图 2 (a) 所示。模块 1是这三个模块中最具挑战性的部分,主要用于满足逻辑控制和高压驱动电路的性能要求。值得注意的是,我们首次提出了一种协同设计的掺杂工程方案,该方案共同优化了 GaN 外延层生长的热工艺与注入杂质分布。与我们之前的工作相比,该协同设计的掺杂工程方案有效抑制了 P 阱的穿通效应(PT),提高了击穿电压,并且关键地实现了对阈值电压的精确调控。栅氧化层下 NMOS 的掺杂剖面分布如图 2 (b) 所示。作为界面工艺,模块 2负责提供高质量的选择性 AlGaN/GaN 外延层,其关键特性是与硅工艺和 GaN 工艺均具备良好的兼容性。模块 3承担了高压 GaN HEMT 的制备任务,并完成了整个工艺链的最终集成。最终,该平台成功集成了包括 5V/20V 低压及高压 CMOS 器件与GaN HEMT在内的多种集成器件。

Fig.1 (a)Cross section of heterogeneous integrated GaN and Silicon devices (b) boundary of selective growth GaN and CMOS region (c) Summary of all heterogeneous devices.

Fig. 2 (a)Process flow of monolithic heterogeneous integrated device platform, (b) comparation of doping engineering of NMOS.

二、 平台化器件

A.

Si区域集成器件的特性表征

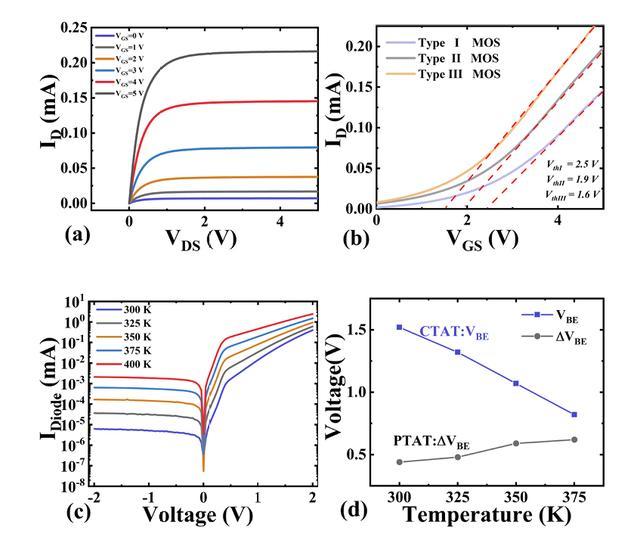

为为评估 GaN/Si CMOS 单片异构集成的可行性,对所制备的所有器件进行了电性能表征。图 3 (a) 和图 3 (b) 分别展示了 NMOS 晶体管的典型输出特性与转移特性。此外,图 3 (b) 还呈现了三种阈值电压(Vth)经过优化的 NMOS 变体的转移特性,其阈值电压范围为 1.6 V 至 2.5 V。图 2 中所示的优化后 NMOS 掺杂剖面同样表明,栅氧化层下方掺杂浓度越低,阈值电压越低,从而制备出一系列满足模拟电路需求的 MOSFET 器件。

对于 DC-DC 变换器控制器而言,温度与电源电压不敏感的基准电压源是不可或缺的。为探究 PN 二极管在基准电路中的应用潜力,本文系统研究了其随温度变化的 I-V 特性。从图 3 (c) 中可清晰观察到,正向导通电流密度与温度呈正相关关系。通过对 I-V 曲线进行拟合计算发现,其开启电压随温度升高而降低。该 PN 结表现出的互补绝对温度(CTAT)系数约为 - 9.33 mV/K,比例绝对温度(PTAT)系数约为 2.4 mV/K,这验证了其适用于带隙基准电压源的设计。

Fig. 3 (a) output characteristics and (b) transfer characteristics of 5V NMOS, (c)temperature dependent IV characteristics of PN diode and (d) CTAT and PTAT voltage for bandgap reference.

B.

GaN区域集成器件的特性表征

图 4 (a) 和图 4 (b) 分别展示了栅宽为 (2×50) μm 的 HEMT 器件的输出特性与转移特性,该器件制备于厚度为 1 μm 的选择性生长 GaN 外延层上。可以观察到,当栅源电压 VGS=1.0 V 时,器件的最大漏极电流达到 300 mA/mm,表明该器件具有高电流密度,约为同类硅基器件的 40 倍。此外,以漏源电流 IDS=1 mA/mm 为定义标准,该器件的阈值电压(VTH)为 - 1.846 V。其比导通电阻(Ron,sp)低至 9.675 mΩ・cm²,表现出优于硅基功率器件的优异性能。

Fig. 4 (a) Output and, (b) transfer characteristics of the HEMT with a gate width of (2×50) μm.

C.

集成器件的建模和参数提取

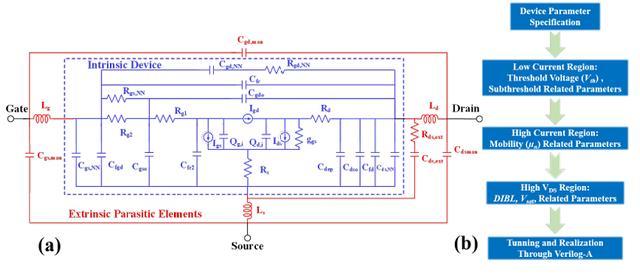

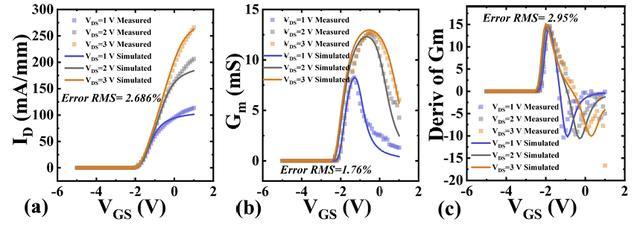

对于 GaN/Si CMOS 单片异构集成系统而言,构建高精度 SPICE 模型是异构集成电路设计与优化的基础前提。本文未采用经验模型,而是选用了高电子迁移率晶体管先进 SPICE 模型(ASM-HEMT)—— 该模型是行业标准的紧凑型非线性物理模型,专门针对 GaN HEMT 器件量身定制。

图 5 展示了器件等效电路,包括本征器件与非本征寄生参数两部分。模型参数提取流程如图 5 所示:首先,在低漏极电流区域提取阈值电压(Vₜₕ)、亚阈值斜率(NFACTOR)以及非线性串联电阻;在高电流区域提取低场迁移率(u0)和场相关迁移率(uA、uB)时,需微调 Vₜₕ和 NFACTOR 以修正电流偏差,提高拟合精度;影响线性区特性的接触串联电阻必须设置为合理数值;随后,在高漏极电压区域提取漏致势垒降低(DIBL)、亚阈值退化以及速度饱和相关参数.

Fig.5 (a)Schematics of GaN ASM-HEMT including intrinsic devices and extrinsic parasitic elements. (b) ASM-HEMT Model Extraction Procedure.

Fig.6 Comparation of simulated data and measured data, (a) transfer characteristics, (b) Gm versus Vgs, (c) derive of transconductance versus Vgs

图 6 给出了 GaN HEMT 器件的测试数据与仿真数据对比。结果表明,脉冲 IV 曲线拟合精度较高,总均方根误差仅为 2.68%,说明 ASM-HEMT 模型能够很好地匹配 HEMT 的电学特性。该集成器件模型基于 Verilog-A 实现,可导出至 Virtuoso 中的 Spectre 仿真器,为后续异构集成电路设计提供支撑。.

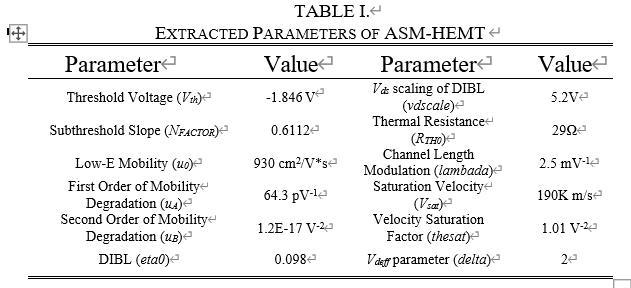

三、DC-DC Buck功率验证

图 7 分别展示了基于全硅、全 GaN 以及 GaN/Si CMOS 异构集成技术的 12 V 转 5 V DC-DC 降压变换器的功率级配置,并对各方案进行了功耗分析。为公平对比不同工艺技术的性能,统一将功率晶体管的导通电阻设定为 300 mΩ,功率器件的栅长统一设定为 1 μm。

对于全硅基功率变换器,其总面积约为 1.94 mm²,这主要归因于其相比 GaN 基方案较低的功率密度。此外,功率晶体管较大的栅电容引入了显著的开关损耗(Psw),其占总损耗(673.62 mW)的比例高达 71.2%。

相比之下,全 GaN 功率级的面积显著减小,仅为 0.021 mm²,较全硅变换器的 1.94 mm² 实现了大幅缩减。然而,尽管开关损耗从 480 mW 降至 24 mW,其总功率损耗仍高达 752.68 mW。这一现象的原因在于,全 GaN 栅极驱动电路采用直流 FL(DCFL)逻辑而非 CMOS 逻辑,导致其功耗较大。图 7 (b) 所示的由 HEMT 器件构成的 DCFL 逻辑会产生显著的静态功耗,从而阻碍了 GaN 器件性能优势的充分发挥。

Fig.7 Schematics of Buck Converter and power consumption analyses (a) all-silicon, (b) all-GaN, (c) GaN/Si CMOS heterogenous integrated..

基于本文提出的先进 GaN/Si CMOS 异构集成平台,成功实现了一款更小、更高效且更灵活的降压变换器。该变换器将硅基 CMOS 控制逻辑、高功率密度 GaN 开关器件与开启电压为 0.7 V 的硅基二极管(作为整流器件)集成一体,从而充分发挥了 GaN 器件的固有优势。所提出的变换器总面积与全 GaN 方案相当(0.023 mm²),而总功率损耗则从全 GaN 方案的 752.68 mW 降至 183.41 mW,实现了集成度与低功耗的双重优化。

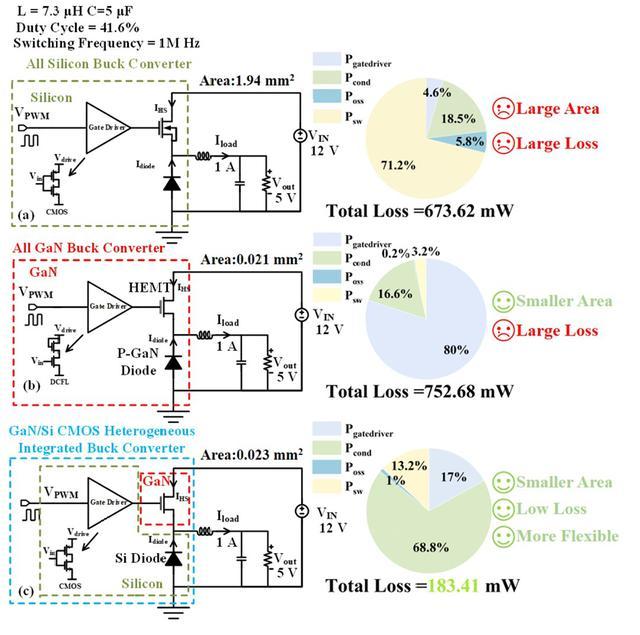

图 8 展示了所设计的 GaN/Si CMOS 异构集成 DC-DC 降压变换器功率级在脉冲宽度调制(PWM)模式下的工作波形。在 1 A 负载条件下,系统稳定工作于 PWM 模式,周期为 1000 ns,对应工作频率(fsw)为 1 MHz。输出电压(Vout)稳定在 5 V,纹波仅为 10 mV,表现出优异的工作稳定性。因此,作为一种先进的 GaN/Si CMOS 集成技术,本文提出的全集成变换器芯片,为人工智能(AI)应用领域中高频、高功率密度电力电子器件提供了一种极具潜力的解决方案。

Fig.8 Schematics of Buck Converter and power consumption analyses (a) all-silicon, (b) all-GaN, (c) GaN/Si CMOS heterogenous integrated.

结 论

基于搭建的6 英寸 GaN/Si CMOS 单片异质集成工艺平台,团队开展硅基 CMOS 工艺与材料集成的协同设计研究,进一步建立可靠的 SPICE 模型及电路实现方案。通过集成 ASM-HEMT 模型,实现了对异构器件的精准表征,为后续电路设计提供了有力支撑。将硅基 CMOS 驱动电路、硅基整流二极管与 GaN 开关器件进行集成,有效克服了全 GaN 方案(静态功耗高)与全Si方案(功率密度低)的固有局限性。该异构集成平台充分发挥了各器件的协同优势,显著提升了集成密度与开关性能。得益于 GaN/Si CMOS 异构工艺中材料集成与工艺集成的深度融合,所制备的原型器件表现出优异的综合性能,这也证实了该方案在人工智能(AI)应用领域的高性能电力电子系统中具有广阔的应用前景。

融正配资提示:文章来自网络,不代表本站观点。